Designing with Versal AI Engine : Architecture and Design Flow (1)

Course Description

This course describes the AMD Versal™ AI Engine architecture, how to program the AI Engines (single kernel programming and multiple

kernel programming using data flow graphs), the data communications between the PL and AI Engines, and how to analyze the kernel program using various debugger features.

The emphasis of this course is on:

- Describing the AI Engine (AIE) architecture

- Illustrating the Versal AI Engine tool flow

- Designing with single AI Engine kernels using the Vitis™ unified software platform

- Designing with multiple AI Engine kernels using data flow graphs with the Vitis Unified IDE

- Reviewing the data movement between AI Engines, between AI Engines via memory and DMA, and between AI Engines to programmable logic (PL)

- Analyzing and debugging kernel performance

- Describing the AIE-ML architecture

- Illustrating the programming model for the AIE-ML

What’s New for 2023.2

- New modules:

▪ Introduction to the AIE-ML Architecture

▪ AIE-ML Memory Tiles and Programming - New lab:

▪ AI Engine-ML Programming Model - All the labs have been updated to the latest software versions

- Tool flow has been revamped for the new Vitis™ Unified IDE

Level

ACAP 2

Course Duration

2 day

Audience

Software and hardware developers, system architects, and anyone who needs to accelerate their software applications using our devices

Prerequisites

- Comfort with the C/C++ programming language

- Software development flow

- Vitis software for application acceleration development flow

Software Tools

- Vitis unified software platform 2023.2

Hardware

- Architecture: Versal adaptive SoCs

Skills Gained

After completing this comprehensive training, you will have the necessary skills to:

- Describe the AMD Versal adaptive SoC architecture at a high level

- Describe the various engines in the Versal device and the motivation behind the AI Engine

- Describe the architecture of the AI Engine

- Describe the memory access structure for the AI Engine

- Describe the full application acceleration flow with the AMD Vitis Unified IDE

- Enumerate the toolchain for Versal AI Engine programming

- Explain what AI Engine APIs are

- Program a single AI Engine kernel using the Vitis tool

- Program multiple AI Engine kernels using adaptive data flow (ADF) graphs

- Describe the architecture of the AIE-ML

- Describe the programming model for the AIE-ML

Course Outline

Day 1

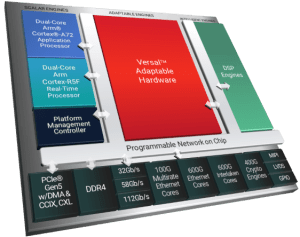

- Overview of the AMD Versal Adaptive SoC Architecture – Provides an overview of the Versal architecture at a high level and describes the various engines in the Versal device, such as the Scalar Engines, Adaptable Engines, and Intelligent Engines. Also describes how the AI Engine in the Versal device meets many dynamic market needs. {Lecture}

- Versal AI Engine Architecture – Introduces the architecture of the AI Engine and its components. {Lecture}

- AI Engine Interfaces – Describes the AI Engine interfaces that are available, including the memory, lock, core debug, cascaded stream, and AXI-Stream interfaces. {Lecture}

- Versal AI Engine Memory and Data Movement – Describes the memory module architecture for the AI Engine and how memory can be accessed by the AI Engines in the AI Engine arrays. {Lecture}

- Versal Adaptive SoC: Application Partitioning 1 – Covers what application partitioning is and how an application can

be accelerated by using various compute engines in the Versal device. Also describes how different models of computation (sequential, concurrent, and functional) can be mapped to the Versal adaptive SoC. {Lecture} - Versal AI Engine Tool Flow – Reviews the Vitis tool flow for the AI Engine and demonstrates the full application acceleration flow for the Vitis platform. {Lecture, Labs}

- Scalar and Vector Data Types – Provides an AI Engine functional overview and identifies the supported vector data types and high-width registers for allowing single-instruction multiple-data (SIMD) instructions. {Lecture}

- AI Engine APIs – Describes what AI Engine APIs are, the three types of vector manipulation operations using AI Engine APIs (load and store, element conversion, and lane insertion/extraction), multiplication functions, and application-specific functions. {Lecture}

- IO Buffers and Streaming Data APIs – Discusses the input/output buffers and streaming data APIs and reviews the various buffer operations for kernels. {Lecture}

- Analyzing AI Engine Design Reports Using the Vitis Unified IDE – Describes the different reports generated by the tool and how to view the reports that help to optimize and debug AI Engine kernels using the Analysis view in the Vitis Unified IDE. {Lecture}

- The Programming Model: Single Kernel – Reviews the AI Engine kernel programming flow for programming and building a single kernel. Also illustrates the steps to create, compile, simulate, and debug a single kernel program using the Vitis Unified IDE. {Lecture, Lab}

Day 2

- The Programming Model: Single Kernel Using Vector Data Types – Illustrates Versal AI Engine kernel programming in detail, reviewing the scalar kernel code and comparing with vector kernel code that utilizes AI Engine APIs and vector data types. {Lab}

- The Programming Model: Introduction to the Adaptive Data Flow (ADF) Graph – Provides the basics of the data flow graph model and graph input specifications for AI Engine programming. Also reviews graph input specifications, such as the number of platforms and ports. {Lecture}

- The Programming Model: Multiple Kernels Using Graphs – Describes the ADF graph in detail and demonstrates the steps to create a graph and set the runtime ratio and graph control APIs from the main application program. {Lecture, Lab}

- Introduction to the AIE-ML Architecture – Introduces the architecture of the AIE-ML at different levels, such as the array, tiles, and components. {Lecture}

- AIE-ML Memory Tiles and Programming – Describes the memory tiles in the AIE-ML architecture and illustrates AI Engine-ML programming using both shared buffers and external buffers with the AIE-ML. {Lecture, Lab

Datum

17 september 2024 - 18 september 2024

Locatie

Core|Vision

Cereslaan 24

5384 VT

Heesch

Prijs

€ 2.000,00

of

20 Xilinx Training Credits

Informatie

Training brochure