Designing FPGAs Using the Vivado Design Suite 1

Course Description

This course offers introductory training on the Vivado® Design Suite and helps you to understand the FPGA design flow.

The course provides experience with:

- Creating a Vivado Design Suite project with source files

- Simulating a design

- Performing pin assignments

- Applying basic timing constraints

- Synthesizing and implementing

- Debugging a design

- Generating and downloading a bitstream onto a demo board

Level

Level

FPGA 1

Course Duration

2 days

Audience

Digital designers new to FPGA design who need to learn the FPGA design.cycle and the major aspects of the Vivado Design Suite

Prerequisites

- Basic knowledge of the VHDL or Verilog language

- Digital design knowledge

Recommended Recorded Videos

- Basic FPGA Architecture: Slice and I/O Resources

- Basic FPGA Architecture: Memory and Clocking Resources

Software Tools

- Vivado System Edition 2019.1

Hardware

- Architecture: UltraScale™ and UltraScale+ FPGAs*

- Demo board (optional): Zynq UltraScale+ ZCU104 board*

* This course focuses on the UltraScale and UltraScale+ architectures. Check with your local Authorized Training Provider for the specifics of the in-class lab board or other customizations.

Skills Gained

After completing this comprehensive training, you will have the necessary skills to:

- Use the New Project Wizard to create a new Vivado IDE project

- Describe the supported design flows of the Vivado IDE

- Generate a DRC report to detect and fix design issues early in the flow

- Use the Vivado IDE I/O Planning layout to perform pin assignments

- Explore synthesis and implementation options and directives

- Synthesize and implement the HDL design

- Apply clock and I/O timing constraints and perform timing analysis

- Describe the “baselining” process to gain timing closure on a design

- Use the Schematic and Hierarchy viewers to analyze and cross-probe a design

- Use the Vivado logic analyzer and debug flows to debug a design

Course Outline

Day 1

- Introduction to FPGA Architecture, 3D IC, SoC {Lecture}

- UltraFast Design Methodology: Board and Device Planning {Lecture, Demo}

- HDL Coding Techniques {Lecture}

- Introduction to Vivado Design Flows {Lecture}

- Vivado Design Suite Project Mode {Lectures, Lab}

- Behavioral Simulation {Lecture}

- Synthesis and Implementation {Lecture, Lab}

- Basic Design Analysis in the Vivado IDE {Lab, Demo}

- Vivado Design Rule Checks {Lab}

- Vivado Design Suite I/O Pin Planning {Lecture, Lab}

- Vivado IP Flow {Lecture, Lab, Demo}

Day 2

- Introduction to Clock Constraints {Lecture, Lab, Demo}

- Generated Clocks {Lecture, Demo}

- I/O Constraints and Virtual Clocks {Lecture, Lab}

- Timing Constraints Wizard {Lecture, Lab}

- Introduction to Vivado Reports {Lecture, Demo}

- Setup and Hold Timing Analysis {Lecture}

- Xilinx Power Estimator Spreadsheet {Lecture, Lab}

- Introduction to FPGA Configuration {Lecture}

- Introduction to the Vivado Logic Analyzer {Lecture, Demo}

- Introduction to Triggering {Lecture}

- Debug Cores {Lecture}

- Introduction to the Tcl Environment {Lecture, Lab}

- Using Tcl Commands in the Vivado Design Suite Project Flow {Lecture, Demo}

- Tcl Syntax and Structure {Lecture}

Topic Descriptions

Day 1

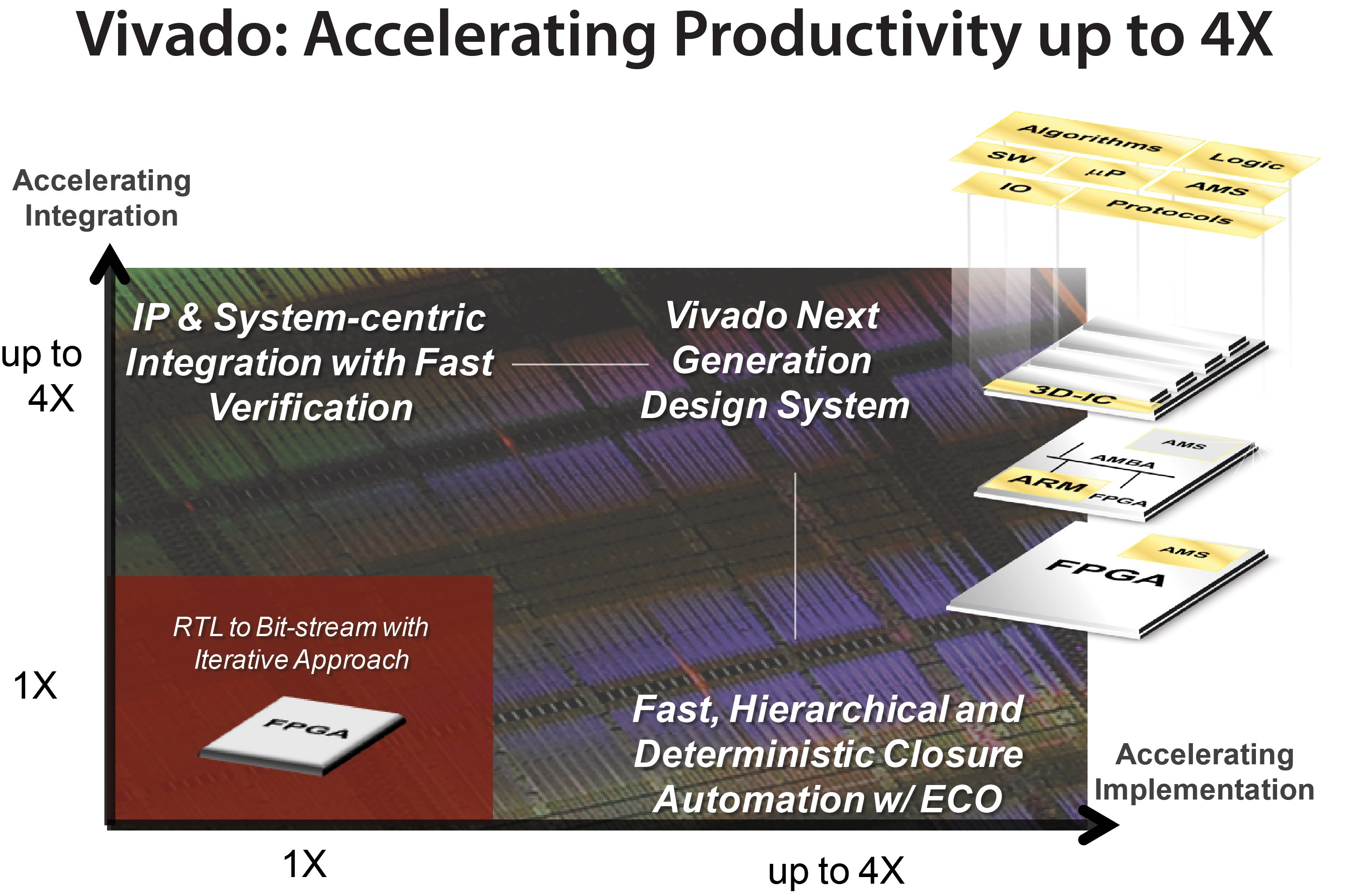

- Introduction to FPGA Architecture, 3D IC, SoC –Overview of FPGA architecture, SSI technology, and SoC device architecture.

- UltraFast Design Methodology: Board and Device Planning –Introduces the methodology guidelines covered in this course and the UltraFast Design Methodology checklist.

- HDL Coding Techniques –Covers basic digital coding guidelines used in an FPGA design.

- Introduction to Vivado Design Flows –Introduces the Vivado design flows: the project flow and non-project batch flow.

- Vivado Design Suite Project Mode –Create a project, add files to the project, explore the Vivado IDE, and simulate the design.

- Behavioral Simulation -Performs behavioral simulation for your design.

- Synthesis and Implementation –Create timing constraints according to the design scenario and synthesize and implement the design. Optionally, generate and download the bitstream to the demo board.

- Basic Design Analysis in the Vivado IDE –Use the various design analysis features in the Vivado Design Suite

- Vivado Design Rule Checks –Run a DRC report on the elaborated design to detect design issues early in the flow. Fix the DRC violations.

- Vivado Design Suite I/O Pin Planning –Use the I/O Pin Planning layout to perform pin assignments in a design.

- Vivado IP Flow –Customize IP, instantiate IP, and verify the hierarchy of your design IP

Day 2

- Introduction to Clock Constraints –Apply clock constraints and perform timing analysis.▪

- Generated Clocks –Use the report clock networks report to determine if there are any generated clocks in a design.▪

- I/O Constraints and Virtual Clocks –Apply I/O constraints and perform timing analysis.▪

- Timing Constraints Wizard –Use the Timing Constraints Wizard to apply missing timing constraints in a design.▪

- Introduction to Vivado Reports –Generate and use Vivado timing reports to analyze failed timing paths.▪

- Setup and Hold Timing Analysis –Understand setup and hold timing analysis.▪

- Xilinx Power Estimator Spreadsheet –Estimate the amount of resources and default activity rates for a design and evaluate the estimated power calculated by XPE.▪

- Introduction to FPGA Configuration –Describes how FPGAs can be configured.▪

- Introduction to the Vivado Logic Analyzer –Overview of the Vivado logic analyzer for debugging a design.▪

- Introduction to Triggering –Introduces the trigger capabilities of the Vivado logic analyzer.▪

- Debug Cores –Understand how the debug hub core is used to connect debug cores in a design.▪

- Introduction to the Tcl Environment –Introduces Tcl (tool command language).▪

- Using Tcl Commands in the Vivado Design Suite Project Flow –Explains what Tcl commands are executed in a Vivado Design Suite project flow.▪

- Tcl Syntax and Structure –Understand the Tcl syntax and structure.

Datum

20 januari 2020 - 21 januari 2020

Locatie

Core|Vision

Cereslaan 24

5384 VT

Heesch

Prijs

€ 0,00

of

18 Xilinx Training Credits

Informatie

Training brochure

Registratieformulier

Registratie op aanvraag, neem contact op met ons.