Online Workshop: Getting started with Xilinx Versal ACAP devices

✅ Indicates CONFIRMED TO RUN

Workshop Description

This free workshop is an introduction how to use the Xilinx Versal™ ACAP architecture and design methodology.

The emphasis of this workshop is on:

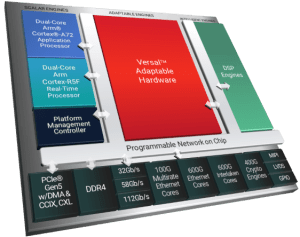

- Reviewing the architecture of the Versal ACAP

- Describing the different engines available in the Versal architecture and what resources they contain

- Using the design tools and methodology provided by Xilinx to create complex systems

- Describing the network on chip (NoC) and AI Engine concepts and their architectures

Workshop Duration

- Duration: 1 day

- Time: 09:00 – 16:00 CET

Audience

Software and hardware developers, system architects, and anyone who wants to learn about the architecture of the Xilinx Versal ACAP device.

Workshop Outline

- 09:00 – 09:30 Introduction – Talks about the need for Versal devices and gives an overview of the different Versal families.

- 09:30 – 10:00 Architecture Overview – Provides a high-level overview of the Versal architecture, illustrating the various engines available in the the Versal architecture.

- 10:00 – 10:15 Break

- 10:15 – 11:00 Design Tool Flow – Maps the various engines in the Versal architecture to the tools required and describes how to target them for final image assembly.

- 11:00 – 11:30 Adaptable Engines (PL) Describes the logic resources available in the Adaptable Engine.

- 11:30 – 12:00 Processing System – Reviews the Cortex™-A72 processor APU and Cortex-R5 processor RPU that form the Scalar Engine. The platform management controller (PMC), processing system manager (PSM), I/O peripherals, and PS-PL interfaces are also covered.

- 12:00 – 13:00 Break

- 13:00 – 13:30 Clocking Architecture – Discusses the clocking architecture, clock buffers, clock routing, clock management functions, and clock de-skew.

- 13:30 – 14:15 DSP Engine – Describes the DSP58 slice and compares the DSP58 slice with the DSP48 slice. DSP58 modes are also covered in detail.

- 14:15 – 14:30 Break

- 14:30 – 15:30 AI Engine – Discusses the AI Engine array architecture, terminology, and AIE interfaces.

- 15:30 – 16:00 NoC Introduction and Concepts – Covers the reasons to use the network on chip, its basic elements, and common terminology.

Date

21 December 2021

Location

Webinar

Online

Webinar

Price

€ 0,00

Registration form

Registration on demand, please contact us.