Zynq UltraScale+ MPSoC for the System Architect

Course Description

This two-day course is structured to provide system architects with an overview of the capabilities and support for the Zynq® UltraScale+™ MPSoC family.

Level

Level

Embedded System Architect 3

Training Duration

2 days

Audience

System architects interested in understanding the capabilities and ecosystem of the Zynq UltraScale+ MPSoC device.

Prerequisites

- Suggested: Understanding of the Zynq-7000 architecture

- Familiarity with embedded operating systems

Software Tools

- Vivado® Design Suite 2018.3

- May require special Zynq UltraScale+ MPSoC family license

- Hardware emulation environment:

- VirtualBox

- QEMU

- Ubuntu desktop

- PetaLinux

Hardware

- Host computer for running the above software*

* This course focuses on the Zynq UltraScale+ MPSoC architecture. Check with your local Authorized Training Provider for the specifics of the in-class lab environment or other customizations. The 2017.1 version of this class does not use a physical board,.but rather a local emulation environment and the Vivado Design Suite.

Skills Gained

After completing this comprehensive training, you will know how to:

- Effectively use power management strategies and leverage the capabilities of the platform management unit (PMU)

- Identify mechanisms to secure and safely run the system

- Outline the high-level architecture of the devices

- Define the boot sequences appropriate to the needs of the system

Course Outline

Day 1

- Zynq UltraScale+ MPSoC Overview {Lecture}

- Zynq UltraScale+ MPSoC HW-SW Virtualization {Lecture, Lab}

- Introduction to QEMU {Lecture, Demo, Lab}

- Zynq UltraScale+ MPSoC Security and Software Test Library {Lecture}

- Zynq UltraScale+ MPSoC System Protection {Lecture, Lab}

- Zynq UltraScale+ MPSoC Security Features {Lecture, Demo}

Day 2

- Zynq UltraScale+ MPSoC Power Management {Lecture, Demo, Lab}

- Zynq UltraScale+ MPSoC System Coherency {Lecture}

- Zynq UltraScale+ MPSoC DDR and QoS {Lecture, Lab}

- Zynq UltraScale+ MPSoC Boot and Configuration {Lecture, Lab}

- Zynq UltraScale+ MPSoC Ecosystem Support {Lecture}

Topic Descriptions

Day 1

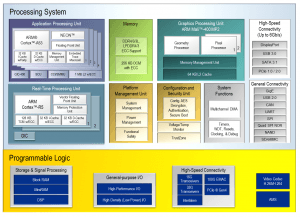

- Zynq UltraScale+ MPSoC Overview – Overview of the Zynq UltraScale+ MPSoC device.

- Zynq UltraScale+ MPSoC HW-SW Virtualization – Covers the hardware and software elements of virtualization. The lab demonstrate how hypervisors can be used.

- Introduction to QEMU – Introduction to the Quick Emulator,.which is the tool used to run software for the Zynq UltraScale+ MPSoC device when hardware is not available.

- Zynq UltraScale+ MPSoC Security and Software Test Library – Introduction to the purpose and API of the Software Test Library.

- Zynq UltraScale+ MPSoC System Protection – Covers all the hardware elements that support the separation of software domains.

- Zynq UltraScale+ MPSoC Security Features – Aspects that implement tamper resistance and control access to the hardware and bitstream.

Day 2

- Zynq UltraScale+ MPSoC Power Management – Overview of the PMU and the power-saving features of the device.

- Zynq UltraScale+ MPSoC System Coherency – Learn how information is synchronized within the API and through the ACE/AXI ports.

- Zynq UltraScale+ MPSoC DDR and QoS {Lecture, Demo, Lab} –.Understand how DDR can be configured to provide the best performance for your system.

- Zynq UltraScale+ MPSoC Boot and Configuration – How to implement the embedded system, including the boot process and boot image creation.

- Zynq UltraScale+ MPSoC Ecosystem Support – Overview of supported operating systems, software stacks, hypervisors, etc.

Datum

16 januari 2019 - 17 januari 2019

Locatie

Core|Vision

Cereslaan 24

5384 VT

Heesch

Prijs

€ 0,00

of

18 Xilinx Training Credits

Informatie

Training brochure

Registratieformulier

Registratie op aanvraag, neem contact op met ons.