Zynq UltraScale+ MPSoC for the Hardware Designer

Course Description

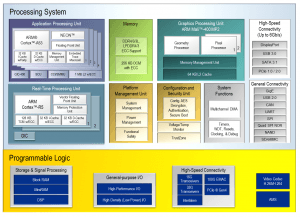

This one-day course is structured to provide hardware designers with an overview of many of the capabilities and support for the Zynq® UltraScale+™ MPSoC family from a hardware architectural perspective.

Level

Level

Embedded Hardware 3

Training Duration

1 day

Who Should Attend?

Hardware designers interested in understanding the architecture and capabilities of the Zynq UltraScale+ MPSoC device

Prerequisites

- Suggested: Understanding of the Zynq-7000 architecture

- Basic familiarity with embedded software development using C (to support testing of specific architectural elements)

Software Tools

- Vivado® Design Suite 2016.3

- May require special Zynq UltraScale+ MPSoC family license

- Hardware emulation environment:

- VirtualBox

- QEMU

- Ubuntu desktop

- PetaLinux

Hardware

- Host computer for running the above software*

* This course focuses on the Zynq UltraScale+ MPSoC architecture. Check with your local Authorized Training Provider for the specifics of the in-class lab environment or other customizations. The 2016.3 version of this class does not use a physical board,.but rather a local emulation environment and the Vivado Design Suite.

Skills Gained

After completing this comprehensive training, you will have the necessary skills to:

- Enumerate the key elements of the application processing unit (APU) and real-time processing unit (RPU)

- List the various power domains and how they are controlled

- Describe the connectivity between the processing system (PS) and programmable logic (PL)

- Utilize QEMU to emulate hardware behavior

Course Outline

- Zynq UltraScale+ MPSoC Application Processing Unit {Lecture, Lab}

- Zynq UltraScale+ MPSoC HW-SW Virtualization {Lecture, Demo, Lab}

- Zynq UltraScale+ MPSoC Real-Time Processing Unit {Lecture, Demo, Lab} QEMU {Lecture, Demo, Lab}

- Zynq UltraScale+ MPSoC Booting {Lecture, Lab}

- Zynq UltraScale+ MPSoC System Protection {Lecture}

- Zynq UltraScale+ MPSoC Clocks and Resets {Lecture, Demo}

- AXI {Lecture, Demo, Lab}

- Zynq UltraScale+ MPSoC PMU {Lecture, Lab}

Topic Descriptions

- Zynq UltraScale+ MPSoC Application Processing Unit – Introduction to the members of the APU, specifically the Cortex™-A53 processor and how the cluster is configured and managed.

- Zynq UltraScale+ MPSoC HW-SW Virtualization – Covers the hardware and software elements of virtualization. The lab demonstrates how hypervisors can be used.

- Zynq UltraScale+ MPSoC Real-Time Processing Unit – Introduction to the various elements within the RPU and different modes of configuration.

- QEMU – Introduction to the Quick Emulator, which is the tool used to run software for the Zynq UltraScale+ MPSoC device when hardware is not available.

- Zynq UltraScale+ MPSoC Booting – How to implement the embedded system, including the boot process and boot image creation.

- Zynq UltraScale+ MPSoC System Protection – Covers all the hardware elements that support the separation of software domains.

- Zynq UltraScale+ MPSoC Clocks and Resets – Overview of clocking and reset, focusing more on capabilities than specific implementations.

- AXI – Understanding how the PS and PL connect enables designers to create more efficient systems.

- Zynq UltraScale+ MPSoC PMU – Overview of the PMU and the power-saving features of the device.

Datum

14 juni 2017

Locatie

Core|Vision

Cereslaan 24

5384 VT

Heesch

Prijs

€ 0,00

of

9 Xilinx Training Credits

Informatie

Training brochure

Registratieformulier

Registratie op aanvraag, neem contact op met ons.