Vitis Model Composer: A MATLAB and Simulink-based Product

✅ Indicates CONFIRMED TO RUN

Course Description

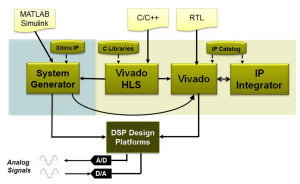

This course provides experience with using the Vitis™ Model Composer tool for model–based designs.

The course provides experience with:

- Creating a model–based design using HDL, HLS, and AIE library blocks along with custom blocks in Vitis Model Composer

- Implementing DSP functions using Vitis Model Composer Utilizing design implementation tools

- Transforming algorithmic specifications to production–quality IP implementations using automatic optimizations and leveraging the high–level synthesis technology of the Vitis HLS tool

- Creating Versal® AI Engine graphs and kernels using Vitis Model Composer

- Connecting AI Engine blocks and non–AI Engine blocks

- Verifying and debugging AI Engine code using the Vitis analyzer

- Simulating and debugging a complex system created using AI Engine library blocks

Level

DSP 3

Course Duration

2 days

Audience

System engineers, system designers, logic designers, and experienced hardware engineers who are implementing Versal AI Engine, HDL, and HLS algorithms using the MathWorks MATLAB® and Simulink® software and want to use Vitis Model Composer

Prerequisites

- Basic experience with the MATLAB and Simulink software

- Basic understanding of DSP designs and sampling theory

- Comfort with the C/C++ programming language for HLS or AI Engine model designs

Software Tools

- Vivado Design Suite 2022.2

- Vitis unified software platform 2022.2

- Vitis HLS tool 2022.2

- MATLAB with Simulink software R2021b

Hardware

- Architecture: UltraScale™ FPGAs and Versal ACAPs*

- Demo board: Zynq® UltraScale+™ MPSoC ZCU104 board*

* This course focuses on the UltraScale and Versal architectures. Check with your local Authorized Training Provider for the specifics of the in–class lab board or other customizations

Skills Gained

After completing this comprehensive training, you will know how to:

- Use optimized HDL, HLS, and AI Engine blocks directly from the Simulink tool library browser

- Create, simulate, and debug a Vitis Model Composer design in the Simulink environment using HDL, HLS, and AIE block libraries

- Perform co–simulation and hardware verification

- Use DSP blocks in Vitis Model Composer to implement DSP functions

- Implement multi–rate systems in Vitis Model Composer

- Design a processor–controllable interface using Vitis Model Composer

- Generate IPs from C–based design sources using the Vitis HLS tool for use in the Vitis Model Composer environment

- Import custom HDL, HLS, and AI Engines code as blocks into Vitis Model Composer

- Generate output products using automatic code generation

- Connect AI Engine blocks and non–AI Engine blocks

- Perform AI Engine code verification using the Vitis analyzer

- Create, simulate, and debug a complex system created using AI Engine library blocks

Course Outline

Day 1

- Introduction to Vitis Model Composer – Introduces the Vitis Model Composer tool and describe the optimized HDL, HLS, and AI Engine library blocks available in Vitis Model Composer. {Lecture}

- Basics of the Simulink Environment – Describes the Simulink software environment, some of the commonly used signal source and sink blocks available in the Simulink software, and how hierarchical designs are created and protected using masked subsystems. {Lecture, Lab} Vitis Model Composer for HDL

- HDL Library in Vitis Model Composer – Illustrates how the HDL library can be used in Vitis Model Composer and how to analyze performance and resource usage in Vitis Model Composer. {Lecture, Lab}

- HDL Library Compilation and Hardware Co–Simulation – Covers how to import HDL modules as well as perform HDL co–simulation and hardware verification. Reviews the compilation types for Vitis Model Composer designs. Also introduces Super Sample Rate (SSR) blocks in Vitis Model Composer. {Lecture}

- DSP Blocks in Vitis Model Composer – Describes the DSP blocks in the HDL and AI Engine library. Also reviews the basics of AXI4 interfaces. {Lecture, Lab}

- Working with Filter Designs – Describes the concept of designing filters supported by Vitis Model Composer. {Lecture, Lab}

- Working with Multi–Rate Systems – Explains how a multi–rate DSP system uses multiple sampling rates within a system. {Lecture}

Day 2

- HLS Library in Vitis Model Composer – Describes how create Vitis Model Composer designs using HLS block libraries, import C/C++ code into Vitis Model Composer, and generate output products using automatic code generation. {Lecture, Labs}

- AI Engine Library in Vitis Model Composer – Demonstrates the usage the AI Engine library in Vitis Model composer for creating an AI Engine design, which involves preparing the kernel and importing the AI Engine code as a block. {Lecture}

- AI Engine Simulation and Code Generation – Illustrates the process of generating AI Engine code with a data flow graph, which involves Simulink simulation with the AI Engine library for functional verification. Also describe the hardware validation flow through generating a hardware image targeting a specific platform for the Simulink environment. {Lecture, Labs}

- Connecting AI Engine and Non–AI Engine Blocks – Explains how to interconnect AI Engine blocks and non–AI Engine (HDL and HLS) blocks. {Lecture}

- Debugging an AI Engine Design in Vitis Model Composer – Shows how to use the Vitis analyzer for viewing and analyzing various parameters that are useful for debugging Versal AI Engines. {Lecture, Lab}

- Exploring Vitis Model Composer Examples in GitHub – Introduces different categories of Vitis Model Composer examples in GitHub and describes the methods to access these examples from GitHub. {Lecture}

Datum

06 september 2023 - 07 september 2023

Locatie

Core|Vision

Cereslaan 24

5384 VT

Heesch

Prijs

€ 0,00

of

20 Xilinx Training Credits

Informatie

Training brochure

Registratieformulier

Registratie op aanvraag, neem contact op met ons.