Designing with the IP Integrator Tool

Course Description

Explore the IP integrator tool and its features to gain the expertise needed to develop, implement, and debug different IPI block designs using the Vivado® Design Suite.

This course focuses on:

- Creating an IPI block design using the Vivado Design Suite

- Creating your own custom IP via the IP packaging flow

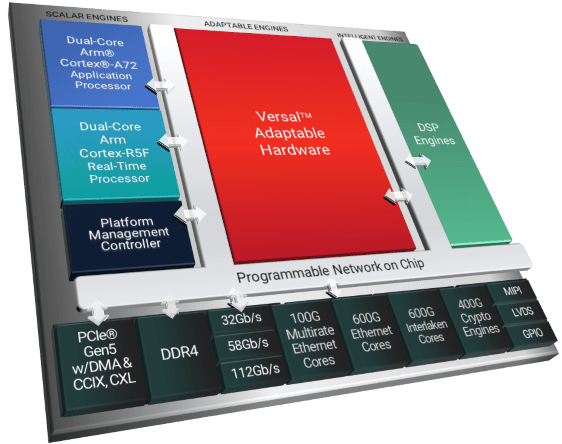

- Using the IP integrator to add and configure the Versal® ACAP CIPS block and then to export the generated programmable device image (PDI)

- Configuring the AXI network on chip (NoC) to access DDR memory controllers in Versal ACAP devices

What’s New for 2022.1

- Designing with the IP Integrator module: Added information on block design module referencing

- All labs have been updated to the latest software versions

Audience

Software and hardware developers, system architects, AI developers and anyone who wants to learn about the IP Integrator tool.

Level

FPGA 1

Training Duration

1 day

Audience

Software and hardware developers, system architects, and anyone who wants to learn about the Vivado Design Suite IP integrator tool

Prerequisites

- Basic FPGA and Vivado Design Suite knowledge

Software Tools

- Vivado Design Suite 2022.1

- Vitis unified software platform 2022.1

Hardware

- Architecture: UltraScale™ family and Versal ACAPs

- Demo board: Zynq UltraScale+ ZCU104 board

Skills Gained

After completing this comprehensive training, you will have the

necessary skills to:

- Describe the Vivado tool flow for RTL–based and IP–based design flows

- Create a Vivado IP integrator block design using the Vivado Design Suite

- Describe the block design container feature in the IP integrator

- Package custom IP and add it to the IP catalog repository or manage it in a remote location

- Use the IP integrator to add and configure the Versal ACAP CIPS block and export the generated hardware

- Configure the AXI NoC to access DDR memory controllers in Versal ACAP devices

- Use a revision control system in the Vivado Design Suite flows

- Use the IP integrator to add debug cores to an existing block design to debug the design

Course Outline

Vivado IP Catalog

- Vivado IP Flow

Customize IP, instantiate IP, and verify the hierarchy of your design IP

IP Integrator

- Designing with the IP Integrator

Use the Vivado IP Integrator to create an IPI subsystem, including a Zynq UltraScale+ MPSoC processing system {Lecture, Demo, Labs} - Block Design Containers in the Vivado IP Integrator

Describe the block design container (BDC) feature and shows how to create a BDC in the IP Integrator {Lecture} - Creating and Packaging Custom IP

Create your own IP and package and include it in the Vivado IP Catalog {Lecture, Lab} - Versal ACAP: Hardware Platform Development Using the Vivado IP Integrator

Describes the different Versal ACAP design flows and covers the platform creation process using the Vivado IP integrator {Lecture, Lab} - Versal ACAP: NoC Introduction and Concepts

Reviews the basic vocabulary and high–level operations of the NoC. {Lecture, Lab}

Debugging

- Debug Flow in an IP Integrator Block Design

Insert the debug cores into IP integrator block designs {Lecture, Lab}

Version Control Systems

- Revision Control Systems in the Vivado Design Suite

Use version control systems with Vivado design flows {Lecture}

Vivado IP Catalog

- Managing IP in Remote Locations

Store IP and related files remote to the current working project directory {Lecture}

Datum

04 januari 2023

Locatie

Core|Vision

Cereslaan 24

5384 VT

Heesch

Prijs

€ 0,00

of

10 Xilinx Training Credits

Informatie

Training brochure

Registratieformulier

Registratie op aanvraag, neem contact op met ons.