Designing FPGAs Using the Vivado Design Suite 4

Course Description

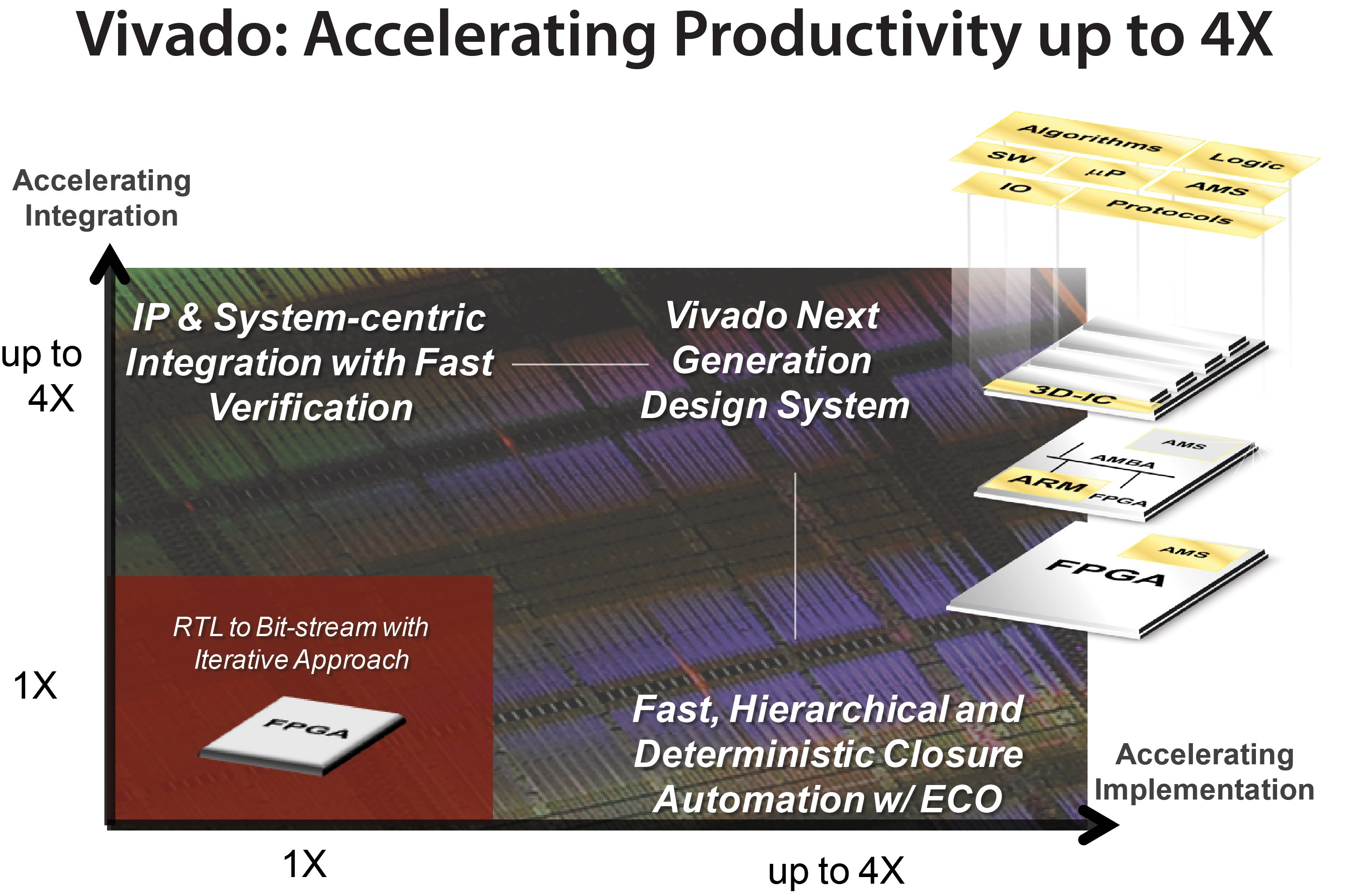

This course tackles the most sophisticated aspects of the Vivado® Design Suite and Xilinx hardware. This course enables you to use the advanced capabilities of the Vivado Design Suite to achieve design closure.

Level

Level

FPGA 3

Course Duration

2 days

Who Should Attend?

Prerequisites

- Designing FPGAs Using the Vivado Design Suite 2 course

- Designing FPGAs Using the Vivado Design Suite 3 course

- At least six months of design experience with Xilinx tools and FPGA

Software Tools

- Vivado System Edition 2017.1

Hardware

- Architecture: UltraScale™ and 7 series FPGAs*

- Demo board (optional): Kintex® UltraScale FPGA KCU105 board or Kintex-7 FPGA KC705 board*

* This course focuses on the UltraScale and 7 series architectures. Check with your local Authorized Training Provider for the specifics of the in-class lab board or other customizations.

Skills Gained

After completing this comprehensive training, you will have the necessary skills to:

- Apply appropriate I/O timing constraints and design modifications for source-synchronous and system-synchronous interfaces

- Analyze a timing report to identify how to center the clock in the data eye

- Use Tcl scripting in non-project batch flows to synthesize, implement, and generate custom timing reports

- Utilize floorplanning techniques to improve design performance

- Employ advanced implementation options, such as incremental compile flow, physical optimization techniques, and re-entrant mode as last mile strategies

- Utilize Xilinx security features, bitstream encryption, and authentication using AES for design and IP security

- Identify advanced FPGA configurations, such as daisy chain and gangs, for configuring multiple FPGAs in a design

- Debug a design at the device startup phase to debug issues related to startup events, .such as MMCM lock and design coming out of reset

Course Outline

Day 1

- UltraFast Design Methodology Introduction 4 {Lecture}

- Scripting in the Non-Project Batch Flow {Lecture, Lab}

- Using Procedures and Lists in Scripting {Lecture}

- Using regexp in Tcl Scripting {Lecture, Lab}

- I/O Timing Scenarios {Lecture}

- Source-Synchronous I/O Timing {Lecture, Lab}

- System-Synchronous I/O Timing {Lecture, Demo}

- Modifying the Clock Edge for Hold Analysis in Multicyle Paths {Lecture, Demo}

- Timing Constraints Priority {Lecture}

- Daisy Chains and Gangs in Configuration {Lecture}

- Managing Remote IP {Lecture, Lab}

- Introduction to Floorplanning {Lecture}

- Design Analysis and Floorplanning {Lecture, Lab}

Day 2

- Incremental Compile Flow {Lecture, Lab}

- Re-entrant Implementation Mode {Lecture, Lab}

- Physical Optimization {Lecture, Lab}

- Trigger and Debug at Device Startup {Lecture, Demo}

- Scripting for a VLA Design {Lecture, Lab}

- ILA Timing Recommendations {Lecture}

- Debug Hub Core Timing Recommendations {Lecture}

- Vivado Design Suite Debug Methodology {Lecture}

- Cross-Triggering Multiple ILAs {Lecture, Lab}

- Power Management Techniques {Lecture}

- eFUSE for Bitstream Security {Lecture, Lab}

Topic Descriptions

Day 1

- UltraFast Design Methodology Introduction 4 – Introduces the methodology guidelines covered in this course.

- Scripting in the Non-Project Batch Flow – Write Tcl commands in the non-project batch flow for a design.

- Using Procedures and Lists in Scripting – Employ procedures and lists in Tcl scripting.

- Using regexp in Tcl Scripting .– Use regular expressions to find a pattern in a text file while scripting an action in the Vivado Design Suite.

- I/O Timing Scenarios .– Overview of various I/O timing scenarios, such as source and system synchronous, direct/MMCM capture, and edge/center aligned data.

- Source-Synchronous I/O Timing. – Apply I/O delay constraints and perform static timing analysis for a source-synchronous, double data rate (DDR) interface.

- System-Synchronous I/O Timing. – Apply I/O delay constraints and perform static timing analysis for a system-synchronous input interface.

- Modifying the Clock Edge for Hold Analysis in Multicyle Paths. – Understand why the clock edge for hold analysis needs to be modified when a multi-cycle path constraint is applied.

- Timing Constraints Priority. – Identify the priority of timing constraints.

- Daisy Chains and Gangs in Configuration – Introduces advanced configuration schemes for multiple FPGAs.

- Managing Remote IP – Store IP and related files remote to the current working project directory.

- Introduction to Floorplanning – Introduction to floorplanning and how to use pblocks while floorplanning.

- Design Analysis and Floorplanning – Explore the pre- and post-implementation design analysis features of the Vivado IDE.

Day 2

- Incremental Compile Flow – Utilize the incremental compile flow when making last-minute RTL changes.

- Re-entrant Implementation Mode – Use re-entrant mode on partial routed nets.

- Physical Optimization – Use physical optimization techniques for timing closure.

- Trigger and Debug at Device Startup – Debug the events around the device startup.

- Scripting for a VLA Design – Use Tcl scripting for VLA designs for adding probes and making connections to probes.

- ILA Timing Recommendations – Understand the impact of using ILA for design timing closure.

- Debug Hub Core Timing Recommendations – Understand the impact of using the debug core hub in design timing closure.

- Vivado Design Suite Debug Methodology – Employ the debug methodology for debugging a design using the Vivado logic analyzer.

- Cross-Triggering Multiple ILAs – Use the cross-triggering feature to trigger multiple ILAs.

- Power Management Techniques – Identify techniques used for low power design.

- eFUSE for Bitstream Security – Use eFUSE for bitstream security.

Datum

30 augustus 2017 - 31 augustus 2017

Locatie

Core|Vision

Cereslaan 24

5384 VT

Heesch

Prijs

€ 0,00

of

18 Xilinx Training Credits

Informatie

Training brochure

Registratieformulier

Registratie op aanvraag, neem contact op met ons.