Comprehensive VHDL

Course Description

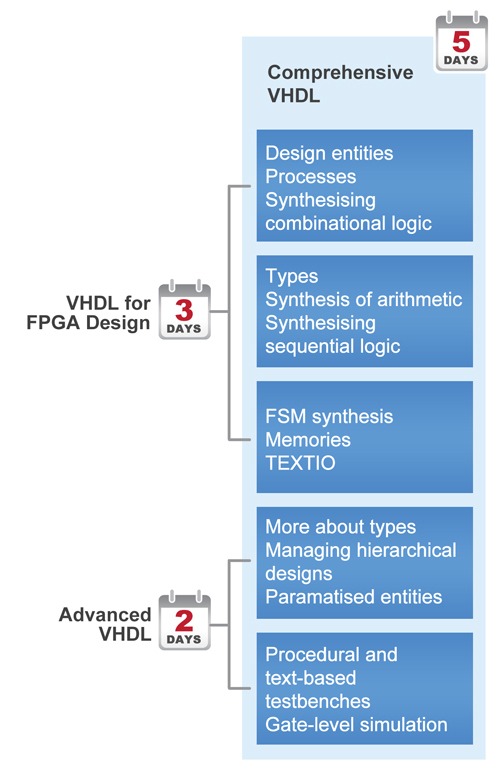

VHDL for Designers (days 1-3) prepares the engineer for practical project readiness for FPGA designs. While the emphasis is on the practical VHDL-to-hardware flow for FPGA devices, this module also provides the essential foundation needed by ASIC and FPGA designers wishing to apply the more advanced features of VHDL covered in the next module. Delegates targeting FPGAs will take away a flexible project infra-structure which includes a set of scripts, example designs, modules and constraint files to use, adapt and extend on their own projects.

VHDL for Designers (days 1-3) prepares the engineer for practical project readiness for FPGA designs. While the emphasis is on the practical VHDL-to-hardware flow for FPGA devices, this module also provides the essential foundation needed by ASIC and FPGA designers wishing to apply the more advanced features of VHDL covered in the next module. Delegates targeting FPGAs will take away a flexible project infra-structure which includes a set of scripts, example designs, modules and constraint files to use, adapt and extend on their own projects.- Advanced VHDL (days 4-5) builds on the foundation of the previous module to prepare the engineer for complex FPGA or ASIC design. It focuses on the use of VHDL for large hierarchical designs, design re-use, and the creation of more powerful test benches.

Workshops comprise approximately 50% of class time, and are based around carefully designed exercises to reinforce and challenge the extent of learning.

Who should attend?

- Engineers who wish to become skilled in the practical use of VHDL for FPGA or ASIC design

- Engineers who are about to embark on the first VHDL design project

- Engineers who have already acquired some practical experience in the use of VHDL, but wish to consolidate and extend their knowledge within a training environment

What will you learn?

VHDL for FPGA Design

- The VHDL language concepts and constructs essential for FPGA design

- How to write VHDL for effective RTL synthesis

- How to target VHDL code to an FPGA device architecture

- How to write simple VHDL test benches

- The tool flow from VHDL through simulation, synthesis and place-and-route

- How to write high quality VHDL code that reflects best practice in the industry

Advanced VHDL

- The VHDL language concepts constructs essential for complex FPGA and ASIC design

- The VHDL language constructs and coding styles that enable sophisticated test benches

- How to code hierarchical designs using multiple VHDL design libraries

- How to write re-usable, parameterisable VHDL code by exploiting generics and data types

- How to run gate-level simulations

Pre-requisites

Delegates must have attended Essential Digital Design Techniques or an equivalent course, or have a good working knowledge of digital hardware design. No previous knowledge of VHDL or a software language is required.

Delegates attending only the Advanced VHDL module must have some hardware design experience, and have completed the VHDL for Designers module or an equivalent course. We have found that delegates frequently overestimate their own capabilities. If in doubt, you will probably benefit from attending the full Comprehensive VHDL course.

Datum

01 mei 2017 - 05 mei 2017

Locatie

Core|Vision

Cereslaan 24

5384 VT

Heesch

Prijs

€ 0,00

of

54 Xilinx Training Credits

Informatie

Training brochure

Registratieformulier

Registratie op aanvraag, neem contact op met ons.